Overview

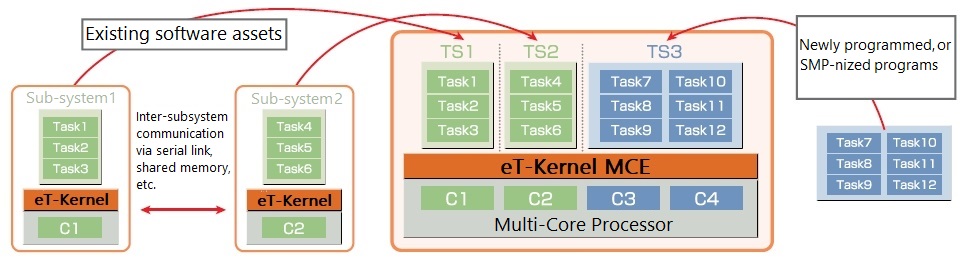

eT-Kernel™ MCE (Multi-Core Edition) is an RTOS for embedded systems using a multi-core processor. It is ideal for next-generation high-performance embedded systems, such as digital household appliances, in-vehicle devices, and mobile devices. Even when using a multi-core processor for the first time, it is equipped with technology allowing re-use of existing software assets, methods for achieving flexible system design, etc. to make the software development process for multi-core processor products run smoothly.

SMP-type programs and AMP-type programs can be mixed

eT-Kernel MCE is an RTOS that allows SMP-type and AMP-type software structures to co-exist within a single OS.

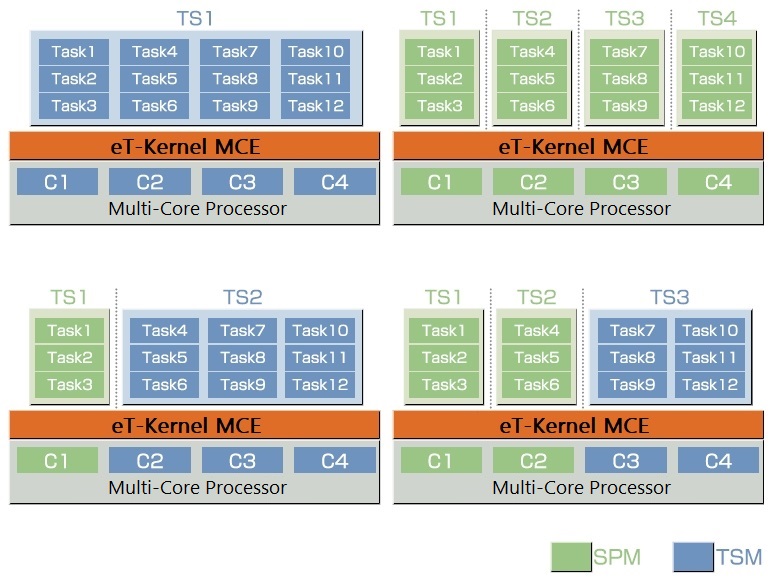

eT-Kernel MCE is equipped with an eSOL-unique scheduling algorithm. This makes it possible to mix multiple SMP-type and AMP-type programs within a single system. Four scheduling modes are available in total, based on “Single Processor Mode (SPM)” and “True SMP Mode (TSM)” basic scheduling modes. By selecting the appropriate mode programmatically, it is possible to enjoy the merits offered by both SMP-type and AMP-type programs within a single system. SMP-type programs offer a high throughput, while AMP-type programs feature remarkable real-time capability and software asset re-usability. Also, since the programs of all CPU cores are controlled with a single OS, special OS services for communication/synchronization between cores are not required.

Using this eT-Kernel MCE scheduling method simultaneously offers the following merits.

Guarantees real-time determinism comparable to single processor

Since an AMP-type program has one CPU core dedicated to it, just as when operating with a single-core processor, the program will execute in a predictable order, guaranteeing real-time behavior for each process within the program.

Top average throughput ensured throughout entire program

An SMP-type program can raise the total average throughput to its highest level. This is ideal for best-effort type programs that do not stress importance on real-time capability for individual processing.

Regular API can be used for communication and synchronization between programs using different CPU cores

When communication/synchronization is to be carried out between programs, the communication/synchronization API offered by the eT-Kernel MCE can be used, which does not distinguish between CPU core differences. Since this API is the same type used for normal tasks, it is not necessary to learn new setups or how to use new API methods. Also, since service is provided through a single OS, the overhead inter-OS communication is no longer present, greatly improving high-speed communication/synchronization.

Reusing existing software assets

Reuse of software assets for a Single-core processor is easy

Even Single-core processor software assets that are not recognized by a multi-core processor can be easily re-used through eT-Kernel MCE’s scheduling method.

eBinder® provides a multi-core processor compatible development environment

By using eBinder, functions and tools can be used efficiently to easily solve the complex issues that are unique to multi-core processor use, while keeping the - same development model as when using a single processor.

This feature contributes to efficient software development for multi-core processors. In addition to debugging individual programs running with each CPU core, this feature also makes it possible to transparently perform tasks such as cooperative operation between programs and full system analysis.

Back to top

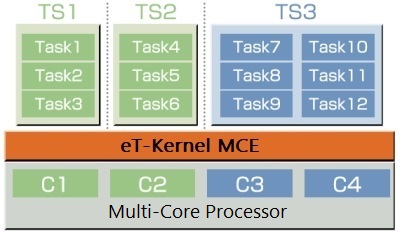

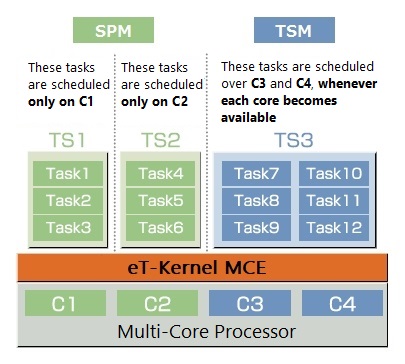

Scheduling method - Blended Scheduling®

An eT-Kernel MCE based system enables users to mix one or multiple AMP-type or SMP-type programs (depending on the quantity within the multi-core processor) with a single multi-core processor and a single eT-Kernel MCE. Because of this, the merits of AMP-type and SMP-type programs can be fully utilized to attain a diverse, flexible system structure. This is made possible by the eT-Kernel MCE’s unique scheduling method. Mode operation for the program is determined during system configuration. A total of four scheduling modes are available as a scheduling method, based on the following two basic modes. A priority-based scheduling method is used for all modes.

Single-Processor Mode (SPM)

Developers can assign a single CPU core to operate the program. Because of this, the program can run on a determined core just as with an AMP-type system.

Merits of SPM

Software assets meant for a single-core processor that are not recognized by multi-core processors can be easily re-used.

- Effective for re-using device drivers. By selecting SPM for embedded processing routine and driver task, and assigning a specific core, single-core drivers can run like before.

- As with single-processor and normal AMP-type systems, non-SPM-type programs that operate with an exclusive CPU core will not run, ensuring the usual real-time capability.

True SMP Mode (TSM)

With this mode, the OS can be used to select a CPU core to operate a program. Program tasks are dynamically allocated to each available core and carried out according to priority level.

Merits of TSM

- Dynamic load sharing via OS.

- The entire program’s average throughput can be raised to its maximum limit.

And two additional scheduling modes are available based on this basic scheduling mode.

Single Processor Mode on TSM cores (SPM on TSM)

This mode allows developers to assign a single CPU core to run a program, from multiple TSM cores that run TSM programs. Because of this, the program will only run with the determined core, but other TSM programs and SRL-on-TSM programs can also run on that core.

Merits of SPM on TSM

- Even if the multi-core processor only has two CPU cores, SMP-type/AMP-type programs can still be mixed.

- Effective for re-using device drivers

When selecting an interrupt process routine, driver task, and SPM on TSM, then assigning a specific core, the driver task spin lock process is no longer necessary. - This reduces CPU idle time which tends to occur frequently with SPM, so that CPU core resources can be utilized effectively

Serialized threads on TSM cores (SRL on TSM)

This mode serializes and runs an assigned task set (normally all tasks belonging to a process). Serialization means that these tasks will not run simultaneously in multiple cores. SPM and SPM on TSM are the same in this respect, but the difference is that cores for running tasks are not fixed, instead spanning over multiple TSM cores. Serialization targets a task set belonging to a certain process, and is not performed for tasks belonging to a different process. Because of this, running multiple processes in this mode will carry out the same serialization as that of a single processor for task groups within the processes. Also, load balancing will be performed in process units for other processes, providing the SMP merit of automatic load sharing.

Merits of SRL on TSM

- SMP scheduling can also be carried out for software assets designed for single-core processors, which are not recognized by multi-core processors.

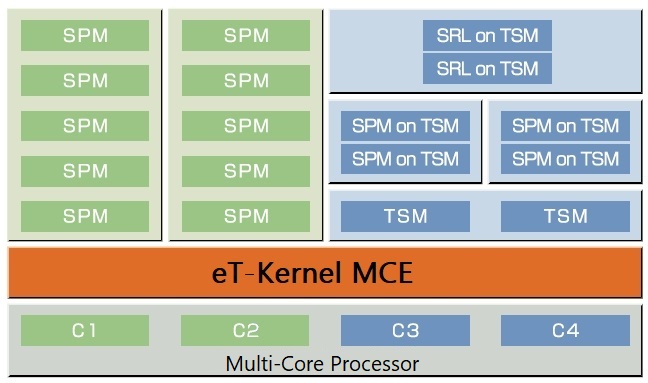

Conceptual Image of SPM on TSM and SRL on TSM

Comparison of 4 scheduling modes

| Scheduling Mode | Executed Core | Thread migration | Load balance | Interference from other cores |

| Single Processor Mode (SPM) |

SPM Core | No | Fixed upon thread creation | None or minimal |

| True SMP Mode (TSM) | TSM Core | Yes | Auto balancing by OS | Yes |

| Single Processor Mode on True SMP (SPM on TSM) |

TSM Core | No | Fixed upon thread creation | Yes |

| Serial on True SMP (SRL on TSM) |

TSM Core | Yes | Fixed upon thread creation | Yes |

System structure example

This system structure example applies when using a multi-core processor with four CPU cores. When using SPM on TSM or SRL on TSM, the pattern will increase even more.

System configuration patterns

Back to top

Easy migration of existing software

By assigning Single Processor Mode (SPM), Single Processor Mode on TSM (SPM on TSM), or Serial on TSM (SRL on TSM), software assets existing on a single processor can quickly and easily be reused with a multi-core processor. This also applies to transition of existing AMP-type programs.

The following image diagram illustrates AMP-type system transition.

| What is SMP? What is AMP? |

|---|

| There are two types of software structures built using a multi-core processor: symmetrical multi-processing (SMP) and asymmetrical multi-processing (AMP). AMP is a function distribution type software structure for a system using multiple CPU cores, which a fixed role assigned to each core, so that each core processes separate programs. On the other hand, SMP does not have a fixed role determined for each CPU core. It is a load sharing type software structure that processes a single program using multiple cores. |

Back to top

| Notes for SMP program structuring |

|---|

| Although an SMP-type program raises total average throughput to its maximum limit, there are several things to note regarding this concept.

Since an SMP-type program is dynamically divided and executed between multiple CPU cores, it is impossible to predict the individual process execution order or which CPU cores are allocated. This means real-time capabilities cannot be fully guaranteed depending on the process. Also, when existing programs for conventional single processors are depending on the priority-based scheduling method to run, low priority programs may only run when a CPU core is available. This and other such issues may occur when using the synchronization or exclusion methods. |

Back to top

| Relationship with TRON Forum’s multi-processor compatible MP T-Kernel |

|---|

| TRON Forum is developing a multi-processor compatible MP T-Kernel. As a managing member of TRON Forum, eSOL has been contributing to the TRON Forum through our know-how and technology refined through the eT-Kernel MCE, actively cooperating to create standard specifications for MP T-Kernel. |

Back to top